# Designing and Verifying Future High Speed Busses

Perry Keller Gregg Buzard

Agilent Technologies FuturePlus Systems

**December 12, 2000**

#### Agenda

- Bus Technology Trends and Challenges

- Making the transition: Design and Test of DDR Busses

- Agilent Technologies and FuturePlus Systems DDR Analysis Solution

- Q&A

#### **Bus Technology Trends**

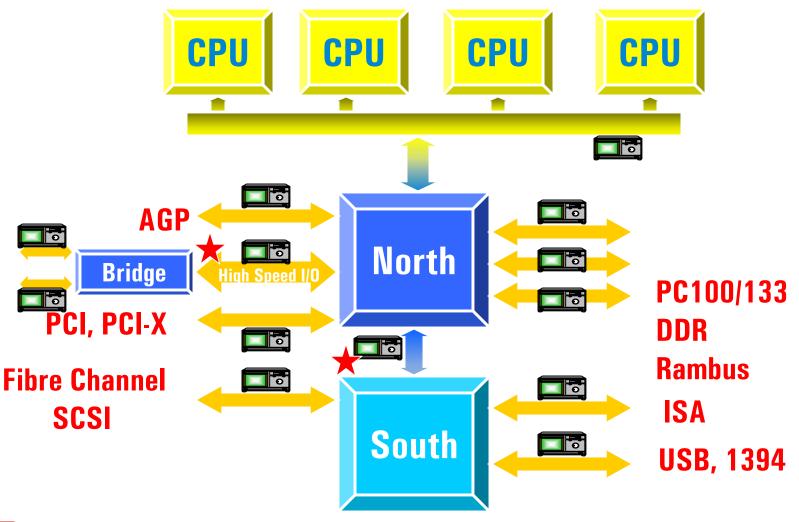

Common Clock → Source Synchronous → Embedded Clock ►SSTL LVDS **→<** 300 mv Single Ended Differential Single Edge ——Double Edge Multipoint/Multidrop ——— Point to Point MC6800 PC133 DDR RapidIO/InfiniBand Fibre Channel PCI PCI-X SCSI 500 MHz 10 MHz 100 MHz 1000 MHz+

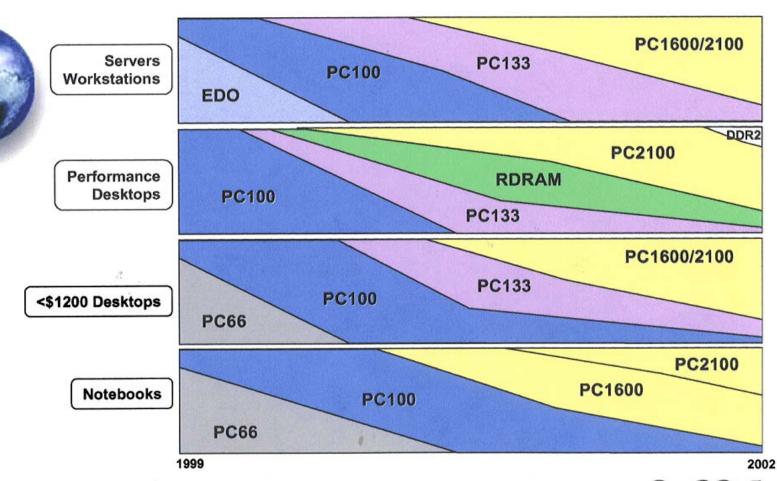

## **Main Memory Demand Forecast**

#### Comparing PC133 and PC266 DDR

|              | PC133      | DDR           |

|--------------|------------|---------------|

| Speed        | 133 Mhz    | 266Mhz+       |

| Clock Edges  | Single     | Double        |

| Clock        | Common     | Source        |

| Method       |            | Synchronous   |

| #Clocks      | 1          | Up to 19      |

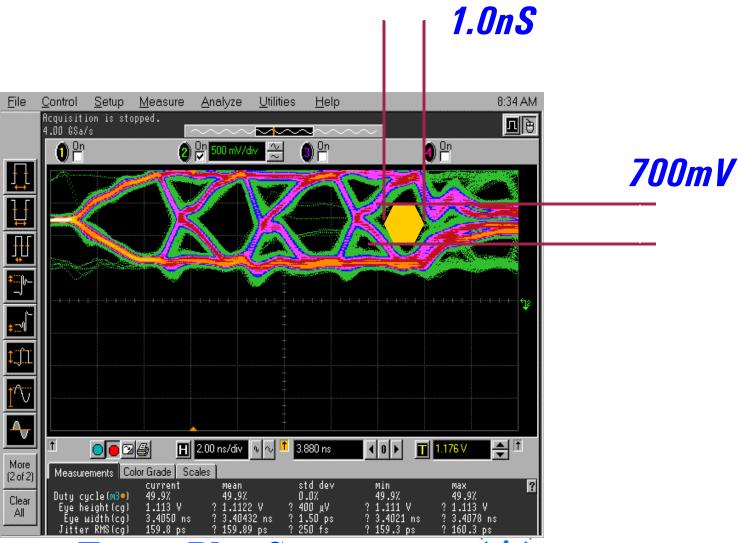

| Eye Size     | 2V x 4ns   | 700mv x 1.0ns |

| Timing       | Centered   | Centered /    |

|              |            | Straddle      |

| Interconnect | Multipoint | Multipoint    |

## DDR Technology Challenge: Finding and Maintaining the Data Eye

- Managing jitter budget

- Crosstalk

- Intersymbol Interference

- Clock **AND** Data Jitter

- Managing signal integrity

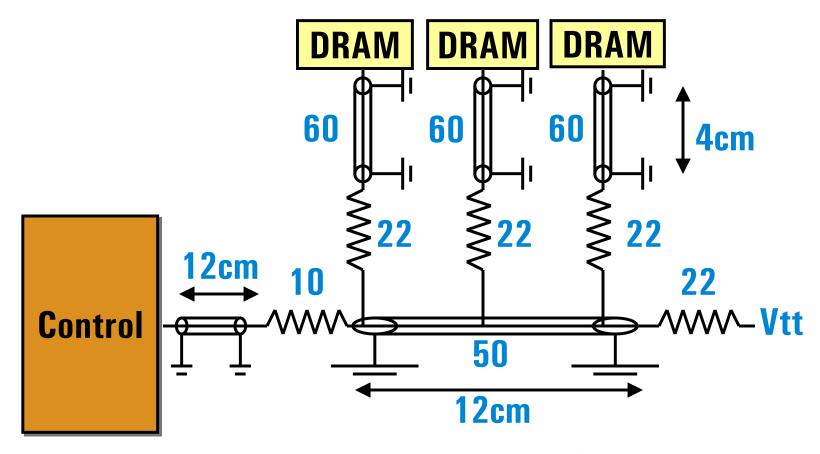

- Termination

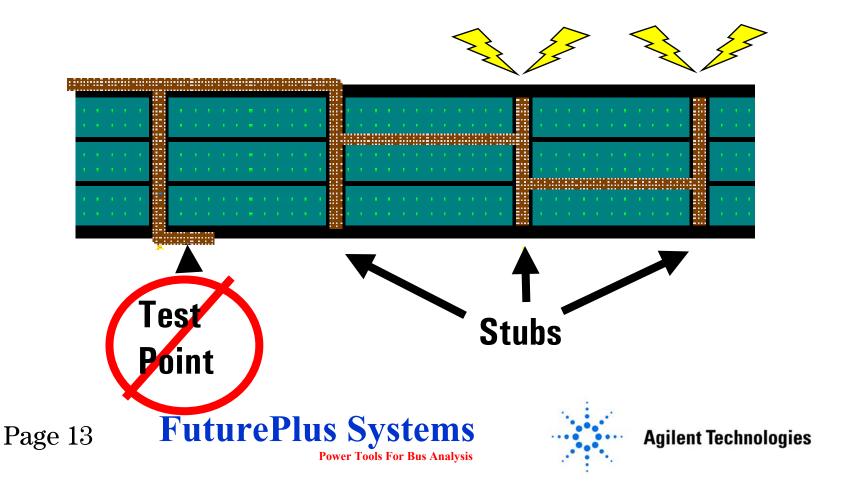

- Stubs

- Signal Loss (Dielectric, Loading)

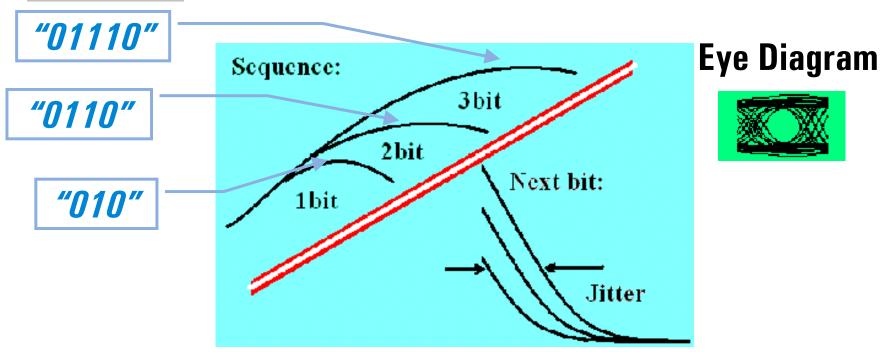

### Sources of Jitter on DDR Bus: Intersymbol Interference

#### Bit pattern

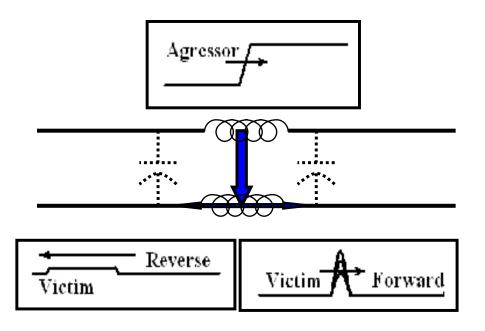

#### Sources of Jitter on DDR Bus: Crosstalk

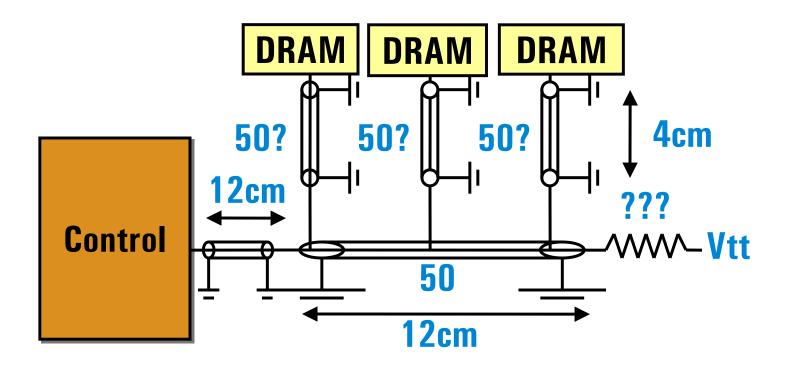

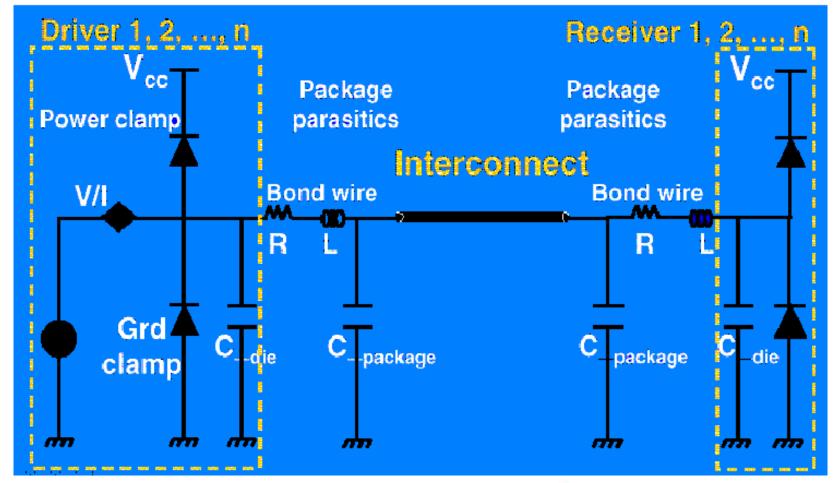

## DDR Bus Signal Integrity: Dealing with Stubs

# DDR Bus - Where to Terminate? Answer: Everywhere! (and Nowhere)

#### **Managing Signal Integrity:**

#### **Spice Simulation**

#### **Optimizing Signal Integrity**

#### **Almost Optimal**

#### **Not Optimal**

#### It's Only Going To Get Worse!

#### Above 1000Mhz vias can become stubs!

#### **DDR Validation - Tools You Will Need**

- Required Tools:

- High Frequency Oscilloscope (1.5Ghz)

- Logic State and Timing Analyzer with DDR Bus Probe

- Spice Simulator

- Useful Tools

- Time Domain Reflectometry (TDR)

- Network Analyzer

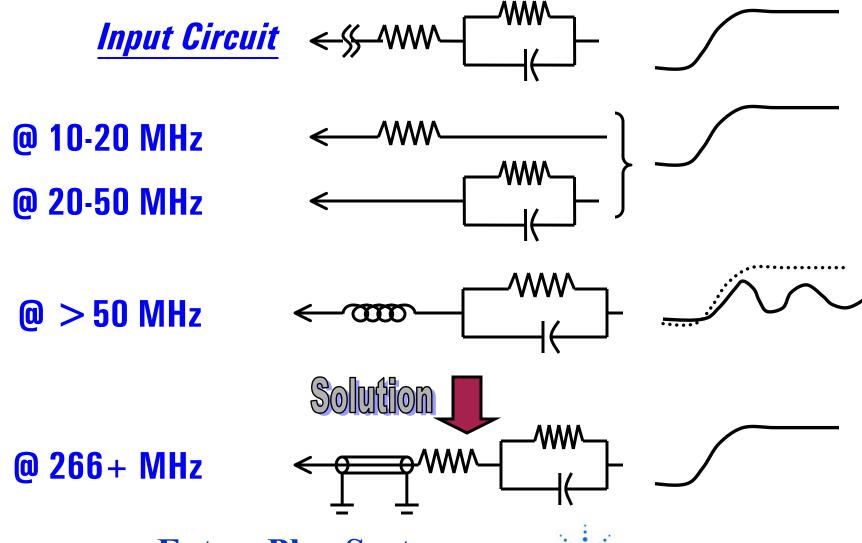

#### **Probing at DDR Frequencies**

Page 15 Futu

FuturePlus Systems

Power Tools For Bus Analysis

**Agilent Technologies**

# Logic Analyzer Sampling - Which Clock to Use?

- Logic Analyzers cannot sample using 19 clocks only one can be chosen

- Skews between Sections may be large

- Traditional solution requires an active probe

# DDR Clock Generation: Where is the real clock edge?

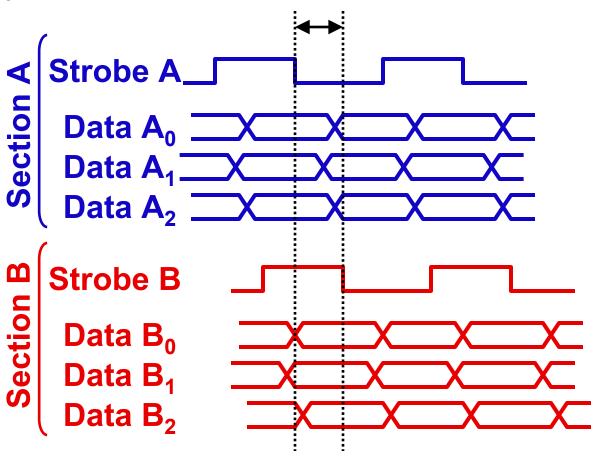

#### **DDR Data Sample Window**

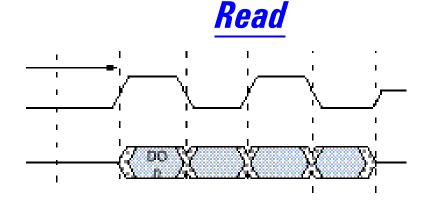

#### **DDR Burst Timing - Read or Write?**

Clock straddles data

Clock centered on data

#### Ideal DDR Analysis Probe

#### **Passive Benefits Active Benefits** +Easy Triggering +Parametric Measurements +Easy Set-up +Low Cost +Higher Speeds **+Early Availability** +Smaller Aperture +Size and +Heat Load **Passive Probe with State Clock Generation**

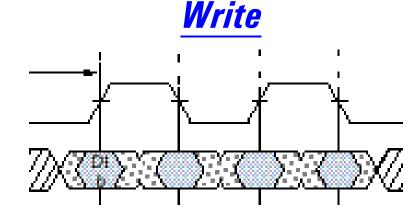

## FS2330 (Agilent FSI-60049) Passive

**DDR Probe**

#### FS2330 (FSI-60049) DDR DIMM

Logic Analyzer Probe

State and Timing **Analysis to PC2662 GHz Timing Analysis** concurrent with State **Analysis**

- Standard DIMM size  $(1.7" \times 5.25")$

- Electrically nonintrusive (same as a 1 bank Registered DIMM)

- Measures signals as the **DDR** memory chips would see them. **FuturePlus Systems**

#### FS2330 Specifications

- All signals are probed passively

- Registered and Non-Registered Dimms supported

- x4 and x8 SDRAMS

- 64 & 72 bit, 2.5V DIMM supported

- Burst size can be set to 2, 4, 8 or automatic

- Select read only/write only acquisition

- External power supply is required and supplied

- Full inverse assembly

- Protocol sensitive clocking

#### FS2330 Logic Analyzer Requirements

- 1675x support

- 2 card (PC200), 3 card (PC266) configuration

- 3 card configuration gives time tags and additional memory depth (8 pods)

- 16715/6/7 Support (PC200, PC266)

- Turbo Mode required 3 card solution minimum

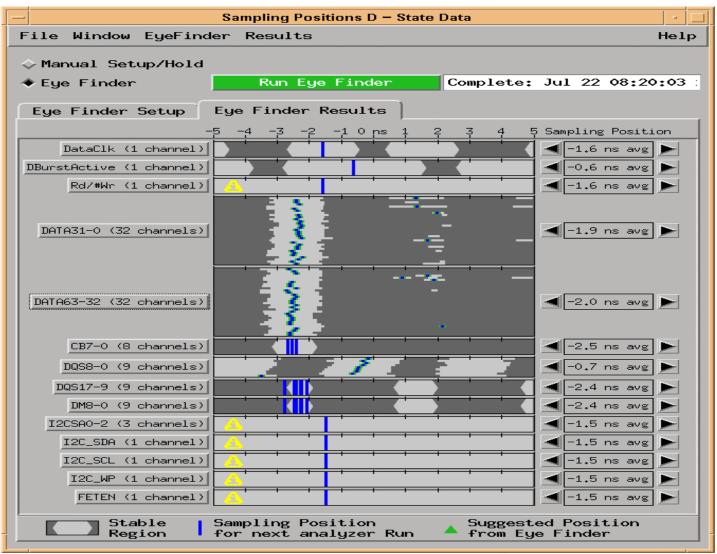

- Eye Finder Technology

- provides characterization

- automatic alignment of clock and data

- 100 psec steps

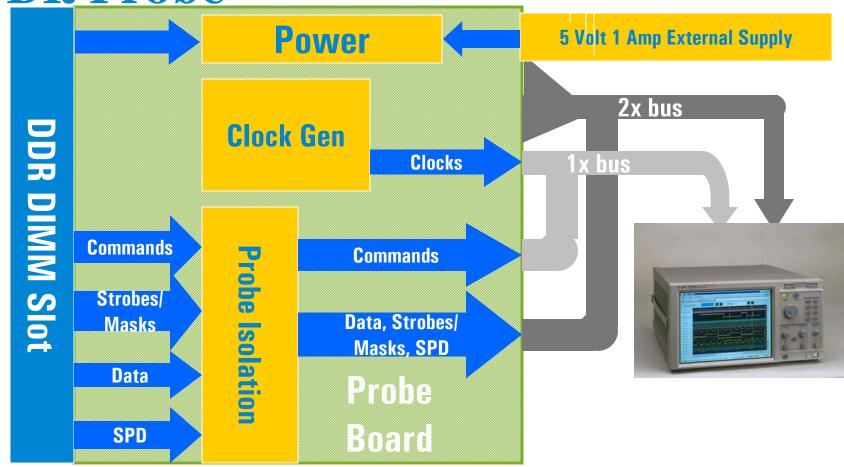

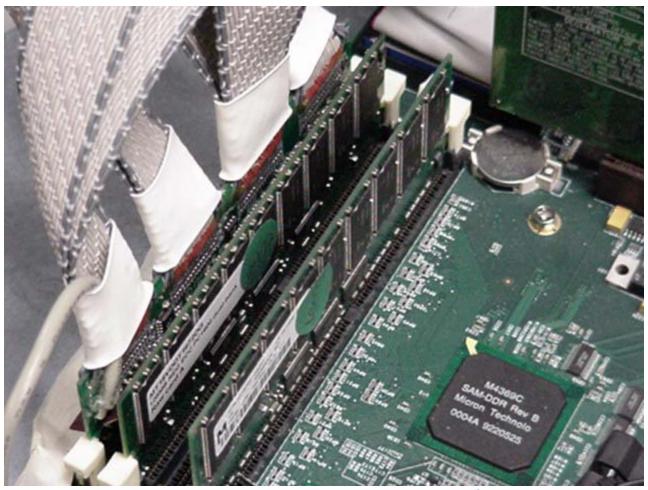

# FS2330 DDR Probe Fits In Standard DIMM Slot

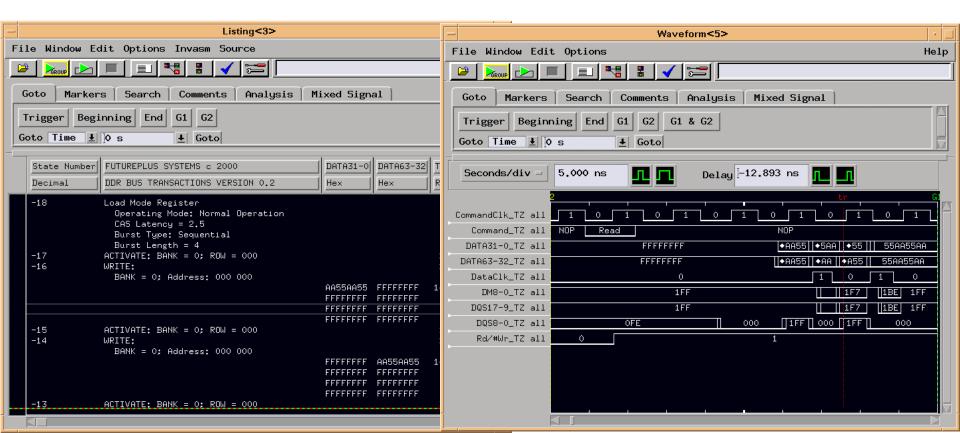

# Simultaneous State and Timing Measurements

• Write Data

Read Bursts

#### **Eye Finder Aligns Clock and Data**

#### **Eye Finder**

- Aligns data and clock in 100 psec increments

- Automatically aligns data and clock

- Shows size of data eye

- Displays signal skews

- Provides timing/phase relationship of bus signals

- Visually shows possible signal integrity problems

- All of the above are QUALITATIVE, not QUANTITATIVE

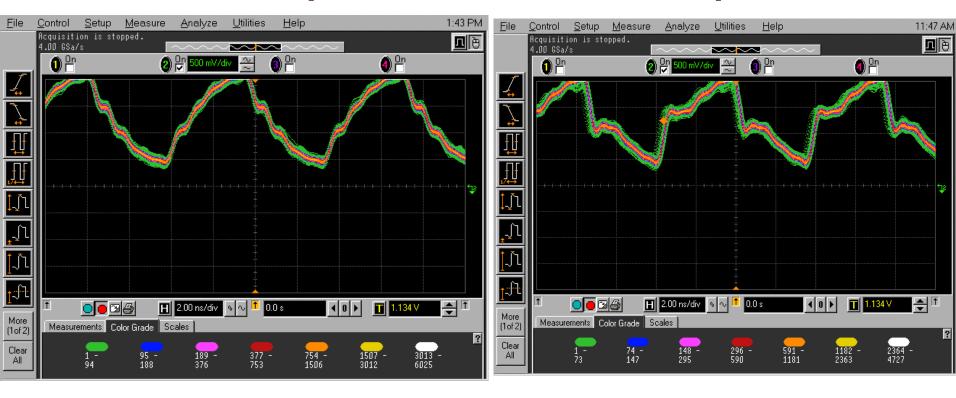

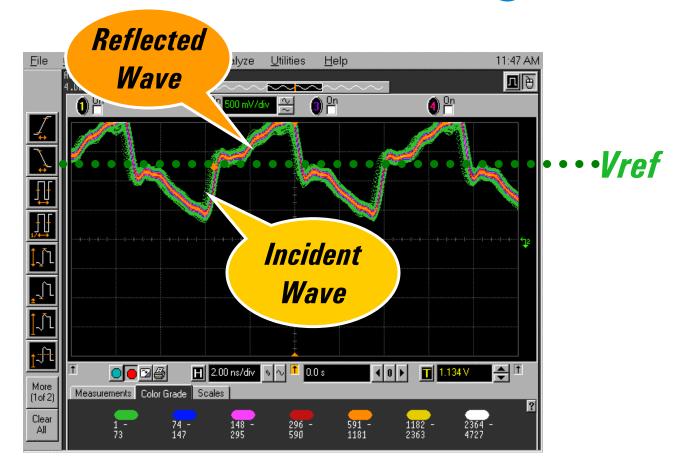

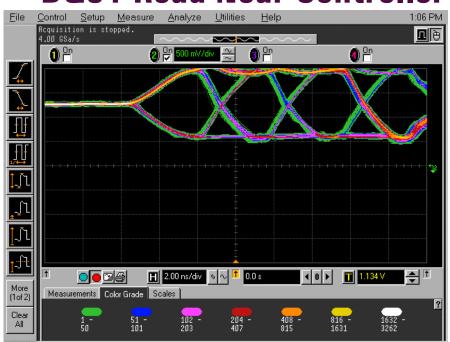

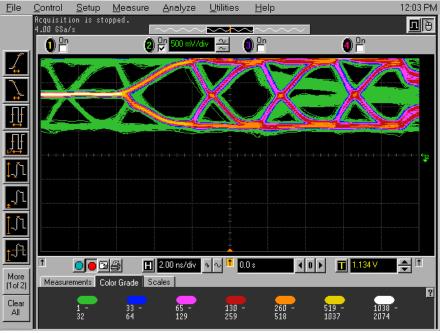

## Reminder In DDR, Signal Integrity is Important -Especially for Reads

#### **DQ51 Read Near Controller**

#### At Far End of Bus

(also write at end of bus)

FuturePlus Systems

Power Tools For Bus Analysis

#### **Summary**

- The high frequency content of DDR demands attention to design issues

- Crosstalk, Intersymbol Interference

- The DDR bus should be treated as transmission lines

- 3D spice modeling

- Terminations, stubs and antennas

#### **Key Points**

- DDR presents new challenges for test tools

- Source Synchronous clocking

- Read/Write timing differences

- Clock detection

- Design debug, verification and validation tools must be transparent to bus

- high speed probing

#### **System Verification**

= Agilent Technologies Logic Analyzers

# Agilent Technologies and FuturePlus Systems

## **Agilent Technologies**

Innovating the HP Way

# **FuturePlus Systems**

**Power Tools For Bus Analysis**